支持指令:lw, sw, beq, bne, addi, add, sub, and, or, slt, j, addi, ori, andi

\framework 为一个支持 lw, sw, beq, bne, addi, add, sub, and, or, slt 的框架,只需要当做填空题补全等号后面的内容即可。

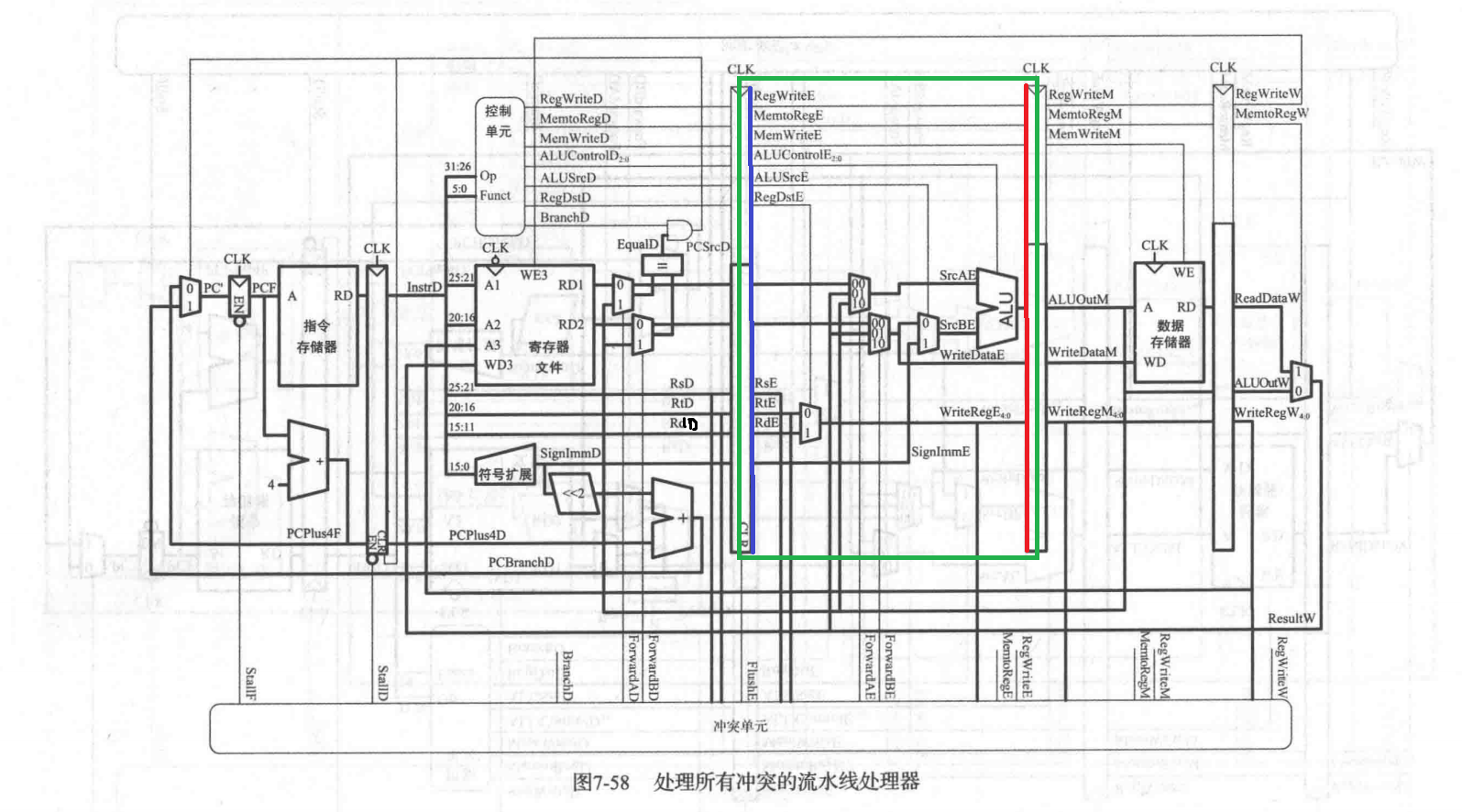

众所周知,MIPS体系的五级流水线CPU分为五个阶段:取指(IF)、译码(ID)、执行(EX)、存储器(MEM)、写回(WB)。所以这根本算不上“设计”,基本上就是把这个图翻译一遍:

举例来说,如下图,执行阶段(EX.sv)描述绿框内的电路,这个模块的输入输出就是所有与绿框有交的节点,输入大致为蓝线上的节点,输出大致为红线上的节点。这里的大致是因为还有一些需要用到的节点是不在这里面的(比如解决冲突连出来的)。

这样做的好处是每个模块独立性较强,几十行代码即可解决,静态查错比较方便;模块间连接也比较规范,很好处理。坏处就是我在赌过了 simulation 后能一遍上板子,还好赌赢了。